AMD Ryzen™ 3000-Series Desktop Prozessor

AMDs größter Wurf kam mit dem Ryzen 3000 Matisse CPU zeitgleich zur Picasso APU am 7. Juni 2019 auf den Markt. AMD überarbeitete die ZEN+ Architektur und separierte die I/O-Einheiten und Speichercontroller aus dem Core-Complex und spendete ihm einen neuen Die. So heißen die Dies des Prozessors bestehend aus einem Multi-Chip-Modul nun Core-Complex-Die und der andere I/O-Die. Das hat den Vorteil, dass man so mehrere Core-Complex-Dies einem I/O-Die zuordnen kann umso einfacher Prozessoren zu skalieren. Zum anderen kann man wie es AMD auch schon macht, auf verschiedene Fertigungsprozesse, Anpassungen und Updates unter den Dies setzen, ohne das Fertigungsverfahren andauernd anpassen zu müssen.

Jeder Core-Complex-Die besteht aus 2 Core-Complex-Einheiten, die jeweils 4 Prozessorkerne enthalten. Der L3-Cache wurde von 8 MByte auf 16 Mbyte pro CCX erhöht. 4 Kerne aus dem Verbund können gemeinsam darauf zugreifen. Die beiden Compute-Complex sind mit dem Infinity-Fabric verbunden. Zusammen hat also jeder Core-Complex-Die 8 CPU-Kerne samt gleicher Anzahl Floating-Point-Units und 32 Mbyte L3-Cache.

AMD konnte durch die ZEN+ zur ZEN2-Architektur die Instructions per Cylce (IPC) in Single-Core Anwendungen auf satte 14 Prozent steigern. In Multi-Core Anwendungen steigen zum Vorgänger die IPC um 16 Prozent. Gegenüber der ersten Ryzen-Generation steigt die Leistung pro Takt sogar um 15 Prozent Single-Core und um 20 Prozent in Multi-Core-Anwendungen.

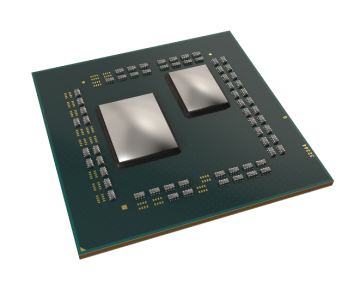

Aufgrund des Aufbaus der Compute-Complex-Dies beinhaltet ein Ryzen 7 mit 8 Kernen abwärts bis Ryzen 5 mit bis zu 6 Kernen einen CCD, der neue Ryzen 9 kommt mit zwei CCDs auf einem Package daher und beinhaltet in Summe 12 – 16 Prozessorkerne sowie einen doppelt multiplizierten L3-Cache von 64 statt 32 Mbyte. Gefertigt sind die Compute-Complex-Dies in 7 nm.

Die I/O-Dies sind für die Kommunikation zwischen Prozessor und Mainboard verantwortlich und beinhalten vieler UnCore-Elemente. Durch die Anbindung des Infinity-Fabrics konnte der I/O-Die baugleich mit dem X570 I/O-Hub auf den Mainboards ausgeführt werden. AMD bestätigte, dass der I/O-Die (IOD) in 12 nm bei Globalfoundries gefertigt wird, weil sich der Fertigungsprozess in 12 nm wesentlich besser für die Speicheranbindung eignet. Der X570 I/O-Hub als Chipsatzlösung wird in 14 nm gefertigt, da dieser keinen aktiven Speichercontroller besitzt.

Technische Daten

| Codename: | Matisse |

|---|---|

| Socket: | Socket AM4 |

| Multi-Core-CPU: | Quad-Core, Hexadeka-Core |

| CPU-Core | Matisse B0, Matisse B0., Matisse B0 |

| Protokoll: | PCIe 4.0 |

| FSB-Takt: | 100 MHz |

| Standard-Takt: | 3100 - 3900 MHz |

| Turbo-Takt: | 3900 - 4700 MHz |

| L1-Cache Instr.: | 4 - 16 x 32 kB |

| L1-Cache Daten: | 4 - 16 x 32 kB |

| L2-Cache: | 4 - 16 x 512 kB |

| L3-Cache: | 16384 - 65536 kB |

| Transistoren: | 5990 - 9890 Mio. |

| Core-Fläche: | 199 - 273 mm˛ |

| Fertigung: | 7 nm |

| Leistungsaufnahme: | 65 - 105 Watt |

| Speicherbandbreite: | 128 Bit Dual-Channel |

| Speichercontroller: | DDR SD-RAM - DDR4-3200 |

| Befehlssätze: | MMX, SSE1 - 4.2, AES, AVX, AVX2, BMI, BMI1+ BMI2, SHA, F16C, SMAP, AMD64, SMEP, Precision Boost 2, SMT, mXFR, Pure Power |

AMD Ryzen 9 Prozessor Package

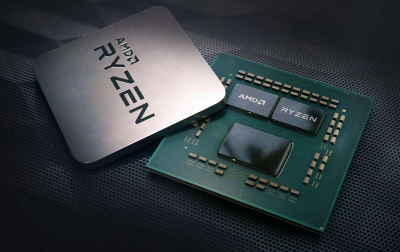

AMD Ryzen Prozessor Package